- 您现在的位置:买卖IC网 > Sheet目录308 > ADZS-BF527-EZLITE (Analog Devices Inc)BOARD EVAL ADSP-BF527

�� �

�

�

�ADSP-BF522/ADSP-BF523/ADSP-BF524/ADSP-BF525/ADSP-BF526/ADSP-BF527�

�length,� and� base� registers� (for� circular� buffering),� and� eight�

�additional� 32-bit� pointer� registers� (for� C-style� indexed� stack�

�manipulation).�

�Blackfin� processors� support� a� modified� Harvard� architecture� in�

�combination� with� a� hierarchical� memory� structure.� Level� 1� (L1)�

�memories� are� those� that� typically� operate� at� the� full� processor�

�speed� with� little� or� no� latency.� At� the� L1� level,� the� instruction�

�memory� holds� instructions� only.� The� two� data� memories� hold�

�data,� and� a� dedicated� scratchpad� data� memory� stores� stack� and�

�local� variable� information.�

�In� addition,� multiple� L1� memory� blocks� are� provided,� offering� a�

�configurable� mix� of� SRAM� and� cache.� The� memory� manage-�

�ment� unit� (MMU)� provides� memory� protection� for� individual�

�tasks� that� may� be� operating� on� the� core� and� can� protect� system�

�registers� from� unintended� access.�

�The� architecture� provides� three� modes� of� operation:� user� mode,�

�supervisor� mode,� and� emulation� mode.� User� mode� has�

�restricted� access� to� certain� system� resources,� thus� providing� a�

�protected� software� environment,� while� supervisor� mode� has�

�unrestricted� access� to� the� system� and� core� resources.�

�The� Blackfin� processor� instruction� set� has� been� optimized� so�

�that� 16-bit� opcodes� represent� the� most� frequently� used� instruc-�

�tions,� resulting� in� excellent� compiled� code� density.� Complex�

�DSP� instructions� are� encoded� into� 32-bit� opcodes,� representing�

�fully� featured� multifunction� instructions.� Blackfin� processors�

�support� a� limited� multi-issue� capability,� where� a� 32-bit� instruc-�

�tion� can� be� issued� in� parallel� with� two� 16-bit� instructions,�

�allowing� the� programmer� to� use� many� of� the� core� resources� in� a�

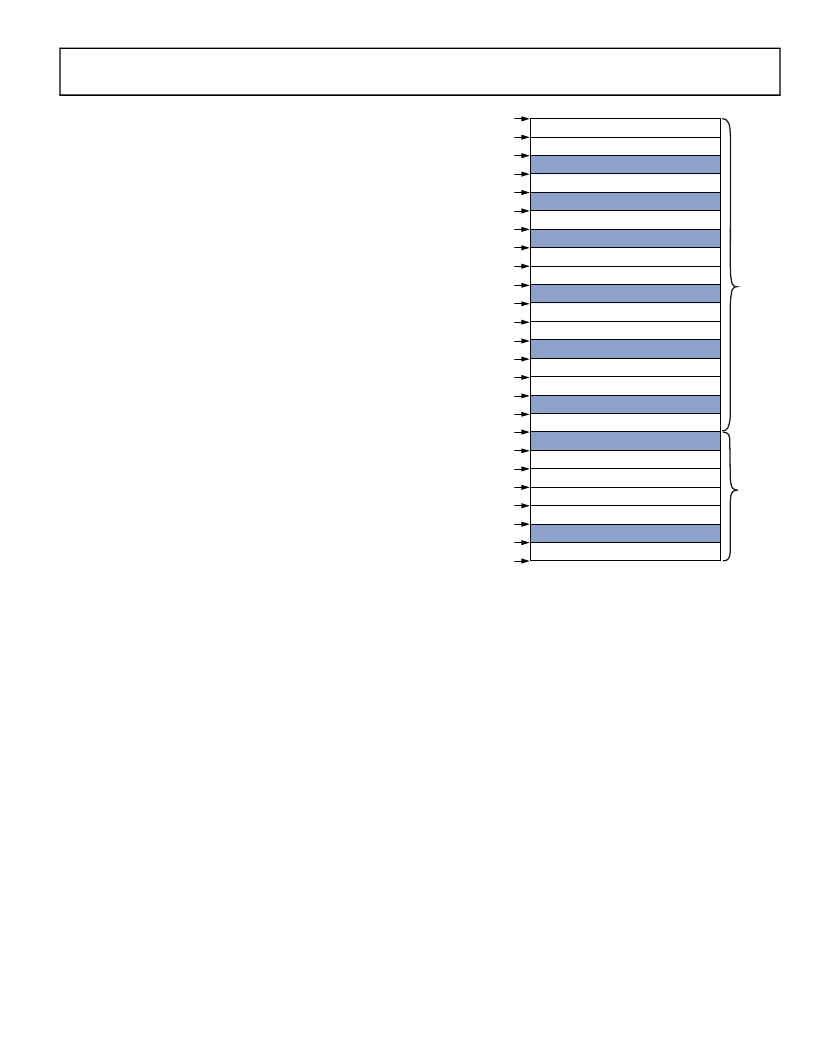

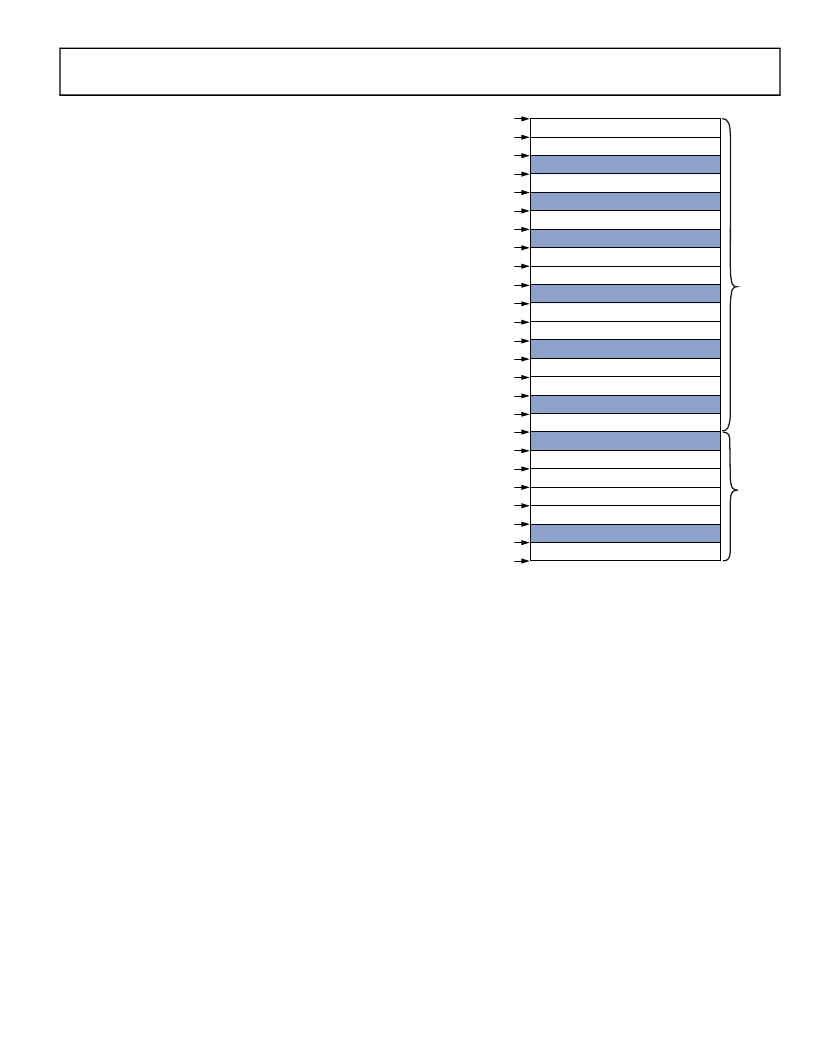

�0xFFFF� FFFF�

�0xFFE0� 0000�

�0xFFC0� 0000�

�0xFFB0� 1000�

�0xFFB0� 0000�

�0xFFA1� 4000�

�0xFFA1� 0000�

�0xFFA0� C000�

�0xFFA0� 8000�

�0xFFA0� 0000�

�0xFF90� 8000�

�0xFF90� 4000�

�0xFF90� 0000�

�0xFF80� 8000�

�0xFF80� 4000�

�0xFF80� 0000�

�0xEF00� 8000�

�0xEF00� 0000�

�0x2040� 0000�

�0x2030� 0000�

�0x2020� 0000�

�0x2010� 0000�

�0x2000� 0000�

�CORE� MMR� REGISTERS� (2M� BYTES)�

�SYSTEM� MMR� REGISTERS� (2M� BYTES)�

�RESERVED�

�SCRATCHPAD� SRAM� (4K� BYTES)�

�RESERVED�

�INSTRUCTION� SRAM� /� CACHE� (16K� BYTES)�

�RESERVED�

�INSTRUCTION� BANK� B� SRAM� (16K� BYTES)�

�INSTRUCTION� BANK� A� SRAM� (32K� BYTES)�

�RESERVED�

�DATA� BANK� B� SRAM� /� CACHE� (16K� BYTES)�

�DATA� BANK� B� SRAM� (16K� BYTES)�

�RESERVED�

�DATA� BANK� A� SRAM� /� CACHE� (16K� BYTES)�

�DATA� BANK� A� SRAM� (16K� BYTES)�

�RESERVED�

�BOOT� ROM� (32K� BYTES)�

�RESERVED�

�ASYNC� MEMORY� BANK� 3� (1M� BYTES)�

�ASYNC� MEMORY� BANK� 2� (1M� BYTES)�

�ASYNC� MEMORY� BANK� 1� (1M� BYTES)�

�ASYNC� MEMORY� BANK� 0� (1M� BYTES)�

�RESERVED�

�single� instruction� cycle.�

�0x08� 00� 0000�

�SDRAM� MEMORY� (16M� BYTES�

�128M� BYTES)�

�The� Blackfin� processor� assembly� language� uses� an� algebraic� syn-�

�tax� for� ease� of� coding� and� readability.� The� architecture� has� been�

�optimized� for� use� in� conjunction� with� the� C/C++� compiler,�

�resulting� in� fast� and� efficient� software� implementations.�

�MEMORY� ARCHITECTURE�

�The� Blackfin� processor� views� memory� as� a� single� unified�

�4G� byte� address� space,� using� 32-bit� addresses.� All� resources,�

�including� internal� memory,� external� memory,� and� I/O� control�

�registers,� occupy� separate� sections� of� this� common� address�

�space.� The� memory� portions� of� this� address� space� are� arranged�

�in� a� hierarchical� structure� to� provide� a� good� cost/performance�

�balance� of� some� very� fast,� low-latency� on-chip� memory� as� cache�

�or� SRAM,� and� larger,� lower-cost� and� performance� off-chip�

��The� on-chip� L1� memory� system� is� the� highest-performance�

�memory� available� to� the� Blackfin� processor.� The� off-chip�

�memory� system,� accessed� through� the� external� bus� interface�

�unit� (EBIU),� provides� expansion� with� SDRAM,� flash� memory,�

�and� SRAM,� optionally� accessing� up� to� 132M� bytes� of�

�physical� memory.�

�The� memory� DMA� controller� provides� high-bandwidth� data-�

�movement� capability.� It� can� perform� block� transfers� of� code�

�or� data� between� the� internal� memory� and� the� external�

�memory� spaces.�

�0x0000� 0000�

�Figure� 3.� Internal/External� Memory� Map�

�Internal� (On-Chip)� Memory�

�The� processor� has� three� blocks� of� on-chip� memory� providing�

�high-bandwidth� access� to� the� core.�

�The� first� block� is� the� L1� instruction� memory,� consisting� of�

�64K� bytes� SRAM,� of� which� 16K� bytes� can� be� configured� as� a�

�four-way� set-associative� cache.� This� memory� is� accessed� at� full�

�processor� speed.�

�The� second� on-chip� memory� block� is� the� L1� data� memory,� con-�

�sisting� of� up� to� two� banks� of� up� to� 32K� bytes� each.� Each� memory�

�bank� is� configurable,� offering� both� cache� and� SRAM� functional-�

�ity.� This� memory� block� is� accessed� at� full� processor� speed.�

�The� third� memory� block� is� a� 4K� byte� scratchpad� SRAM� which�

�runs� at� the� same� speed� as� the� L1� memories,� but� is� only� accessible�

�as� data� SRAM� and� cannot� be� configured� as� cache� memory.�

�External� (Off-Chip)� Memory�

�External� memory� is� accessed� via� the� EBIU.� This� 16-bit� interface�

�provides� a� glueless� connection� to� a� bank� of� synchronous� DRAM�

�(SDRAM),� as� well� as� up� to� four� banks� of� asynchronous� memory�

�devices� including� flash,� EPROM,� ROM,� SRAM,� and� memory�

�mapped� I/O� devices.�

�Rev.� D� |� Page� 5� of� 88� |� July� 2013�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ADZS-BF533-EZLITE

KIT W/BOARD EVAL FOR ADSP-BF533

ADZS-BF538F-EZLITE

BOARD EVAL FOR ADSP-BF538

ADZS-BF561-EZLITE

BOARD EVAL ADSP-BF561

ADZS-BF592-EZLITE

KIT EVAL EZ LITE ADZS-BF592

ADZS-BF609-EZBRD

KIT EVAL EZ-BOARD ADSP-BF60X

ADZS-HPUSB-ICE

TOOL EMULATOR USB HP CROSSCORE

ADZS-ICE-100B

EMULATOR BLACKFIN

AK-Y1301

CABLE SCSI-3 EXTENSION 68CONDUCT

相关代理商/技术参数

ADZS-BF527-EZLITE

制造商:Analog Devices 功能描述:ADSP-BF527 EZ-KIT Lite Evaluation Kit

ADZS-BF527-MPSKIT

功能描述:BOARD EVAL MEDIA PLAYER BF527 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:- 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF)

ADZS-BF533-EZLITE

功能描述:KIT W/BOARD EVAL FOR ADSP-BF533 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

ADZS-BF533-EZLITE

制造商:Analog Devices 功能描述:Microcontroller Development Tool

ADZS-BF533-MMSKIT

功能描述:KIT STARTER MULTIMEDIA BF533 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF)

ADZS-BF537-ASKIT

功能描述:BOARD EVAL SKIT ADSP-BF537 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

ADZS-BF537-EZLITE

功能描述:BOARD EVAL ADSP-BF537 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

ADZS-BF537-STAMP

功能描述:SYSTEM DEV FOR ADSP-BF537 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA